## Dissertation / Doctoral Thesis

Titel der Dissertation / Title of the Doctoral Thesis

## Space-Filling Curves for Improved Cache-Locality in Shared Memory Environments

verfasst von / submitted by

Dipl-Ing. Martin Albin Perdacher, BSc

angestrebter akademischer Grad / in partial fulfillment of the requirements for the degree of Doktor der Technischen Wissenschaften (Dr. techn.)

Wien, 2020 / Vienna, 2020

Studienkennzahl lt. Studienblatt /

UA 786 880

degree programme code as it appears on

the student record sheet:

Studienrichtung It. Studienblatt / degree programme as it appears on

Informatik

the student record sheet:

Betreut von / Supervisor:

Univ.-Prof. Dipl.-Inform.Univ. Dr. Claudia Plant

Betreut von / Supervisor: Prof. Dr. Christian Böhm

#### Abstract

Today's microprocessors consist of multiple cores each of which can perform multiple additions, multiplications, or other operations simultaneously in one clock cycle. In shared memory environments at least two types of parallelism must be applied to exploit the maximum performance of the algorithm: MIMD (Multiple Instruction Multiple Data) where each core simultaneously perform different operations on different types of input data streams and SIMD (Single Instruction Multiple Data) where within a core, the same operation is executed at once on various data. Additionally, modern microprocessors offer a rich memory hierarchy, including various levels of cache and registers. Some of these memories (like main memory, L3 cache) are big but slow and shared among all cores. Others (registers, cache lines, L1 cache) are fast and exclusively assigned to a single core but small. Only if data access has a high locality, we can avoid excessive data transfers between the different levels of the memory hierarchy. Algorithms in linear algebra are often defined by three or more nested loops. In this thesis, we propose to traverse such loops in an order defined by a space-filling curve, such as the Hilbert or the Morton-order curve. The low-level kernels used in this work are based on Advanced Vector Extensions (AVX), which allow the exploitation of several levels of parallelism in shared memory environments. We apply our space-filling curves in several algorithms ranging from linear algebra (matrix-multiplication, Cholesky decomposition, LU factorization) or clustering (K-means) as well as in database queries (i.e., similarity join).

#### Kurzfassung

Heutige Mikroprozessoren bestehen aus mehreren Kernen, von denen jeder mehrere Additionen, Multiplikationen oder andere Operationen gleichzeitig in einem Taktzyklus ausführen kann. In Shared Memory Architekturen müssen zumindest zwei Arten von Parallelität angewendet werden, um die maximale Leistung des Algorithmus auszunutzen: MIMD (Multiple Instruction Multiple Data), bei dem jeder Kern gleichzeitig verschiedene Operationen an verschiedenen Typen von Eingangsdatenströmen ausführt, und SIMD (Single Instruction Multiple Data), bei dem innerhalb eines Kerns dieselbe Operation an verschiedenen Daten gleichzeitig ausgeführt wird. Zusätzlich bieten moderne Mikroprozessoren eine reichhaltige Speicherhierarchie mit verschiedenen Ebenen der Caches für jedes der Register. Einige dieser Speicher (wie Hauptspeicher, L3-Cache) sind groß, aber langsam und werden von allen Kernen gemeinsam genutzt. Andere (Register, Cache-Zeilen, L1-Cache) sind schnell und ausschließlich einem einzigen, aber kleinen Kern zugeordnet. Nur wenn die Datenzugriffe eine hohe Lokalität haben, können übermäßige Datentransfer zwischen den Elementen der Speicherhierarchie vermieden werden. Algorithmen in der linearen Algebra werden oft durch drei oder mehreren verschachtelte Schleifen definiert. In dieser Arbeit schlagen wir vor, solche Schleifen in einer Reihenfolge zu durchlaufen, die durch eine raumfüllende Kurve, wie z.B. die Hilbert- oder die Morton-Ordnung definiert ist. Die in dieser Arbeit verwendeten Low-Level-Kernel basieren auf Advanced Vector Extensions (AVX), die die Ausnutzung auf mehreren Ebenen der Parallelität in gemeinsam genutzten Speicherumgebungen ermöglichen. Wir wenden unsere raumfüllenden Kurven in verschiedenen Algorithmen an, die von linearer Algebra (Matrix-Multiplikation, Cholesky-Zerlegung, LU-Faktorisierung) oder Clustering (K-means) bis hin zu Datenbankabfragen (d.h. Similarity Join) reichen.

### Acknowledgments

I want to thank both advisors Prof. Claudia Plant and Prof. Christian Böhm, for their continuous support, patience, and encouragement during the past years, which shaped my scientific thinking and work. Their precise and efficient work and their scientific advice contributed to the success of this work. I am also very grateful for the excellent working environment at the University of Vienna.

I would also like to thank my wife Eva and my son Viktor in this way. Both of them often had to cut back in order to give me the necessary time for my doctorate. Evas love, her trust and her unbelievably big heart have given me countless times the peace of mind I need for a doctoral program.

Big thanks also to my collegues and friends Ben, Sahar, Lukas, Lena, Ylli, Theresa, Can, Max, Robert, Katerina, and Ewald. Work would be boring without you.

#### Bibliographic Note

Most of the results of this thesis were successfully published in high-profile conference proceedings and journal articles. Therefore, the chapters of this thesis are based on the following publications and manuscripts:

- Chapter 3: Christian Böhm, Martin Perdacher, and Claudia Plant. 'Multicore K-means'. In: *Proceedings of the 2017 SIAM International Conference on Data Mining, Houston, Texas, USA, April 27-29, 2017.* Ed. by Nitesh V. Chawla and Wei Wang. SIAM, 2017, pp. 273–281.

- C. Böhm and M. Perdacher jointly devised the project and the main conceptual ideas and carried out the implementation.

- M. Perdacher additionally performed experiments, discussed and implemented related work.

- C. Plant supervised the project and particularly took care for consistency of the claimed contributions, experimentation, and related work.

- All authors contributed to the development and evaluation of the proposed techniques and to paper writing.

- Chapter 5 and 6: The journal version of the paper:

Christian Böhm, Martin Perdacher, and Claudia Plant. 'A Novel Hilbert Curve for Cache-locality Preserving Loops'. In: *IEEE Transactions on Big Data* (2018), pp. 1–14. ISSN: 2332-7790

and the previous conference version of this paper:

Christian Böhm, Martin Perdacher, and Claudia Plant. 'Cache-oblivious loops based on a novel space-filling curve'. In: 2016 IEEE International Conference on Big Data, BigData 2016, Washington DC, USA, December 5-8, 2016. IEEE Computer Society, 2016, pp. 17–26

- C. Böhm and M. Perdacher jointly developed the main conceptual ideas, proofs and implementation where C. Böhm was responsible for the characteristics of the proposed extension of the space-filling curve ("FUR-Hilbert") and M. Perdacher developed the integration into various application algorithms like Matrix Multiplication and K-means.

- C. Plant supervised the project and particularly took care for consistency of the claimed contributions, experimentation, and related work.

- All authors contributed to the development and evaluation of the proposed techniques and to paper writing.

- Chapter 7: Martin Perdacher, Claudia Plant, and Christian Böhm. 'Cacheoblivious High-performance Similarity Join'. In: Proceedings of the 2019 International Conference on Management of Data, SIGMOD Conference 2019,

Amsterdam, The Netherlands, June 30 July 5, 2019. ACM, 2019, pp. 87–104.

- M. Perdacher and C. Böhm jointly devised the main conceptual ideas and outlined proofs.

- M. Perdacher was additionally responsible for the overall algorithm, performed experiments, and carried out implementation.

- C. Plant supervised the project and particularly took care for consistency of the claimed contributions, experimentation, and related work.

- All authors contributed to the development and evaluation of the proposed techniques and to paper writing.

- Chapter 8: Martin Perdacher, Claudia Plant, and Christian Böhm. 'Improved Data Locality Using Morton-order Curve on the Example of LU Decomposition'. In: 2020 IEEE International Conference on Big Data, BigData 2020, Atlanta, GA, USA, December 10-13, 2020. Accepted for publication. Dec. 2020.

- M. Perdacher devised the proposed algorithms, performed experiments and carried out implementation and discussion.

- C. Plant and C. Böhm supervised the work.

- All authors contributed to the development and evaluation of the proposed techniques and to paper writing.

All authors agreed on this statement of the responsibilities of the individual authors.

# Contents

| $\mathbf{A}$ | bstra                  | ct                                         | i            |

|--------------|------------------------|--------------------------------------------|--------------|

| K            | urzfa                  | ssung                                      | iii          |

| A            | cknov                  | wledgments                                 | $\mathbf{v}$ |

| Bi           | ibliog                 | graphic Note                               | vii          |

| Li           | st of                  | Figures                                    | xiii         |

| Li           | $\operatorname{st}$ of | Tables                                     | xvii         |

| 1            | Intr                   | roduction                                  | 1            |

|              | 1.1                    | Contributions                              | 4            |

|              | 1.2                    | Publications                               | 5            |

|              | 1.3                    | Structure of this Thesis                   | 6            |

| <b>2</b>     | Par                    | allelism in Shared Memory Environment      | 9            |

|              | 2.1                    | SIMD and MIMD                              | 9            |

|              | 2.2                    | Parallelism via Instructions               | 11           |

|              | 2.3                    | Hardware Multithreading                    | 12           |

|              | 2.4                    | General Remarks                            | 13           |

| 3            | Mu                     | lti-core K-means                           | 15           |

|              | 3.1                    | Introduction to a Cache-conscious Approach | 15           |

|              | 3.2                    | K-means                                    | 16           |

|              | 3.3                    | Multi-core K-means                         | 16           |

|              | 3.4                    | Cluster ID Coding                          | 22           |

|              | 3.5                    | Experiments                                | 24           |

$\mathbf{x}$  CONTENTS

|   | 3.6 | Related Work and Discussion                                | 28  |

|---|-----|------------------------------------------------------------|-----|

|   | 3.7 | Conclusion                                                 | 31  |

| 4 | Con | struction of Space-Filling Curves                          | 33  |

|   | 4.1 | Introduction and Historical Context                        | 33  |

|   | 4.2 | Hilbert Function On the Example of Approximating Polygones | 36  |

|   | 4.3 | A Quaternary Hilbert Pattern                               | 37  |

|   | 4.4 | Observations                                               | 39  |

|   | 4.5 | L-systems                                                  | 42  |

|   | 4.6 | Concluding Remarks                                         | 43  |

| 5 | Cac | he-oblivious Hilbert Curve                                 | 45  |

|   | 5.1 | Introduction                                               | 45  |

|   | 5.2 | Locality of the Hilbert Curve                              | 46  |

|   | 5.3 | Well-known Methods for the Hilbert Curve                   | 46  |

|   | 5.4 | Novel Non-recursive Lindenmayer                            | 52  |

|   | 5.5 | Nano-Programs                                              | 59  |

|   | 5.6 | Overall Architecture                                       | 62  |

|   | 5.7 | Concluding Remarks                                         | 63  |

| 6 | App | olications of Cache-oblivious Hilbert Curve                | 65  |

|   | 6.1 | Algorihtms                                                 | 65  |

|   | 6.2 | Experimental Evaluation                                    | 69  |

|   | 6.3 | Related Work and Discussion                                | 80  |

|   | 6.4 | Conclusion                                                 | 83  |

| 7 | Hig | h-Performance Similarity Join                              | 85  |

|   | 7.1 | Introduction                                               | 85  |

|   | 7.2 | Similarity Join                                            | 88  |

|   | 7.3 | Preliminaries                                              | 92  |

|   | 7.4 | The FGF-Hilbert Join                                       | 94  |

|   | 7.5 | Experimental Evaluation                                    | 104 |

|   | 7.6 | Related Work and Discussion                                | 118 |

|   | 7.7 | Conclusion                                                 | 121 |

| 8 | Cac | he-oblivious Morton-order Curve                            | 123 |

|   | 0.1 | Introduction                                               | 123 |

*CONTENTS* xi

|              | 8.2   | Generating Morton-order Curves                                        | 125 |

|--------------|-------|-----------------------------------------------------------------------|-----|

|              | 8.3   | Parallelization                                                       | 134 |

|              | 8.4   | Application of Morton-order Loops for LU Decompositon and Matrix Mul- |     |

|              |       | tiplication                                                           | 135 |

|              | 8.5   | Experimental Evaluation                                               | 139 |

|              | 8.6   | Related Work and Discussion                                           | 145 |

|              | 8.7   | Conclusion                                                            | 148 |

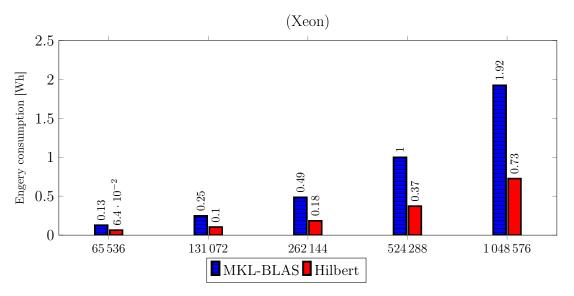

| 9            | Ene   | rgy efficiency on Data Movement                                       | 149 |

|              | 9.1   | ${\bf Introduction} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $           | 149 |

|              | 9.2   | Experimental Setup                                                    | 150 |

|              | 9.3   | Experimental Evaluation                                               | 151 |

|              | 9.4   | Discussion                                                            | 153 |

|              | 9.5   | Conclusion                                                            | 155 |

| 10           | Sum   | nmary and Conclusion                                                  | 157 |

|              | 10.1  | Future work                                                           | 158 |

| Bi           | bliog | raphy                                                                 | 161 |

| $\mathbf{A}$ | Furt  | ther Experiments                                                      | 175 |

|              | A.1   | Runtime Performance on Morton-order Curves                            | 175 |

# List of Figures

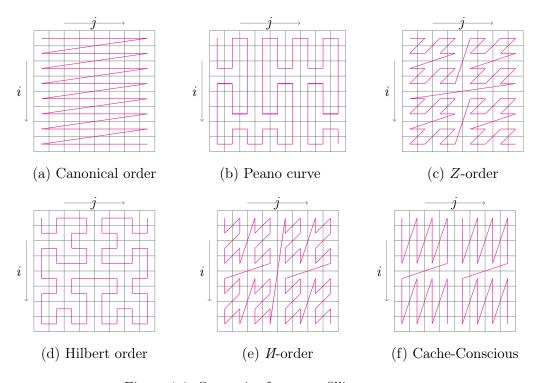

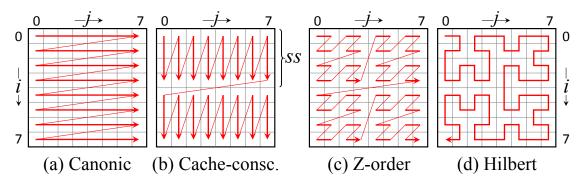

| 1.1 | Strategies for space-filling curves                                                                                                                                                                                               | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | SISD and SIMD paradigm                                                                                                                                                                                                            | 10 |

| 2.2 | MIMD paradigm                                                                                                                                                                                                                     | 11 |

| 3.1 | Loop traversal order over $n, k$ , and $d$                                                                                                                                                                                        | 17 |

| 3.2 | Vertical and Horizontal Addition, Permutation of Vectors                                                                                                                                                                          | 19 |

| 3.3 | Cluster ID coding in IEEE-754 format                                                                                                                                                                                              | 23 |

| 3.4 | Comparison to Standard K-means                                                                                                                                                                                                    | 26 |

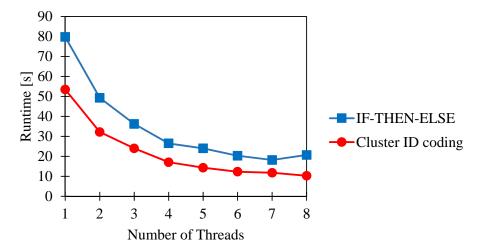

| 3.5 | Speedup with Varying Number of Threads                                                                                                                                                                                            | 27 |

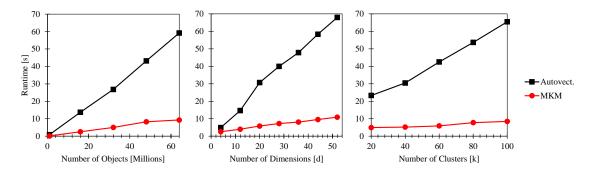

| 3.6 | Effect of Cluster-ID Coding                                                                                                                                                                                                       | 28 |

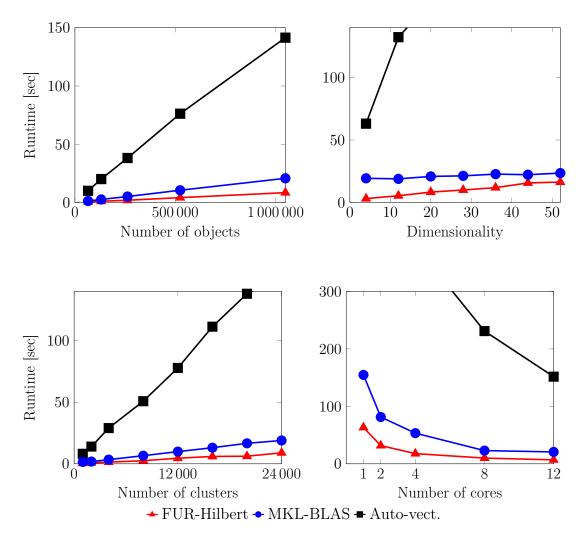

| 3.7 | Scalability of the Different Strategies with $n, d,$ and $k$                                                                                                                                                                      | 28 |

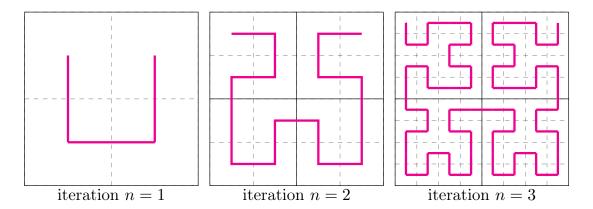

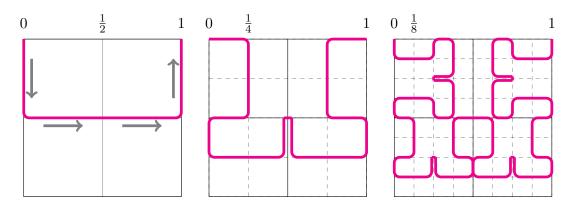

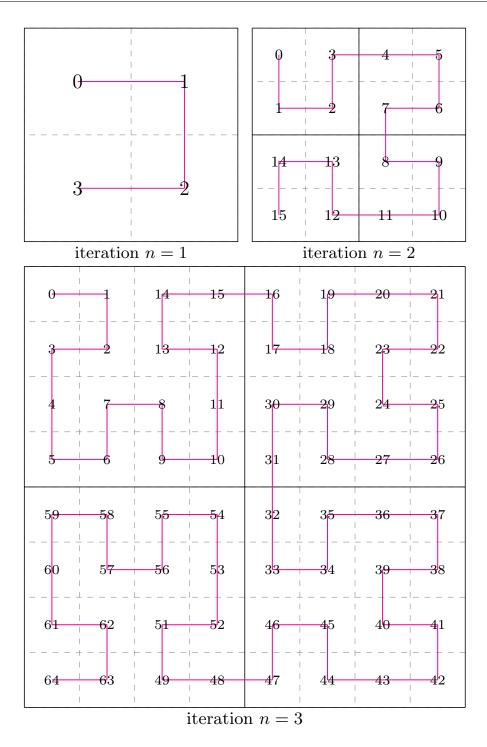

| 4.1 | Iterations of the Hilbert curve.                                                                                                                                                                                                  | 35 |

| 4.2 | First three approximations of the Hilbert curve using polygons                                                                                                                                                                    | 36 |

| 4.3 | The Hilbert value $h$ in decimal format for the first three iterations of the                                                                                                                                                     |    |

|     | Hilbert curve                                                                                                                                                                                                                     | 38 |

| 4.4 | The Hilbert value $h$ in the quaternary format for the first three iterations of                                                                                                                                                  |    |

|     | the Hilbert curve                                                                                                                                                                                                                 | 40 |

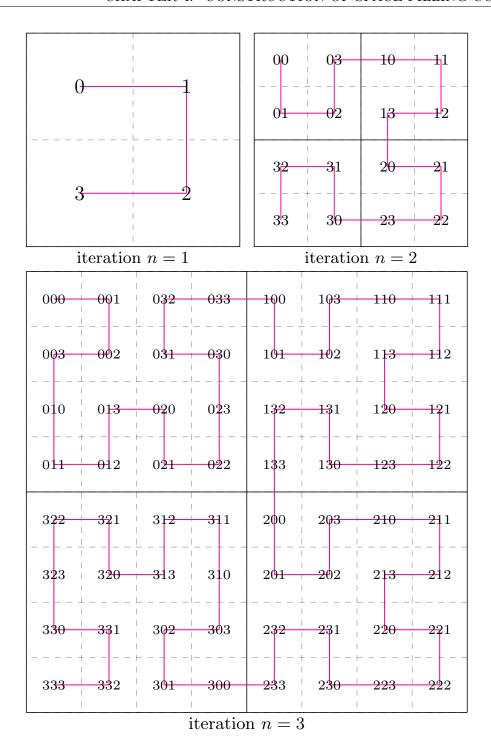

| 5.1 | Comparison of the Traversal Order for Nested Loops (a) and Hilbert Loops (b). An improved locality can be recognized in the histories over time for variable $i$ (c) and $j$ (d), and a considerably improved cache miss rate (e) | 47 |

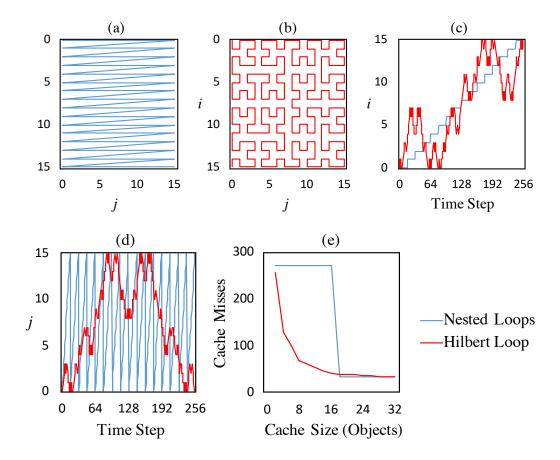

| 5.2 | Mealy-DFA for Inverse Hilbert: $(i, j) := \mathcal{H}^{-1}(h)$ to generate variables $i$ and                                                                                                                                      |    |

| J   | j from the Hilbert value $h$                                                                                                                                                                                                      | 48 |

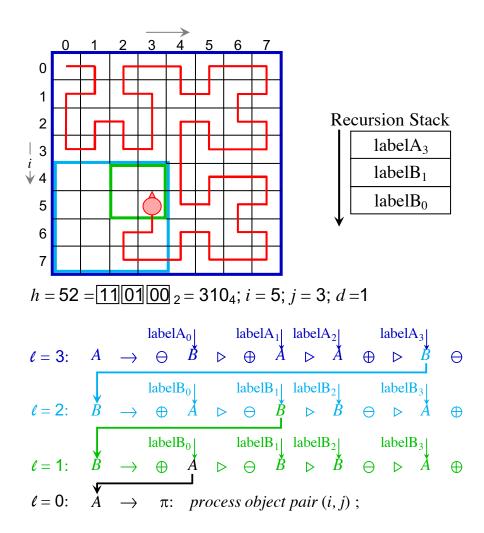

| 5.3 | Recursive generation of $(i, j)$ -pairs following the Hilbert-curve                                                                                                                                                               | 52 |

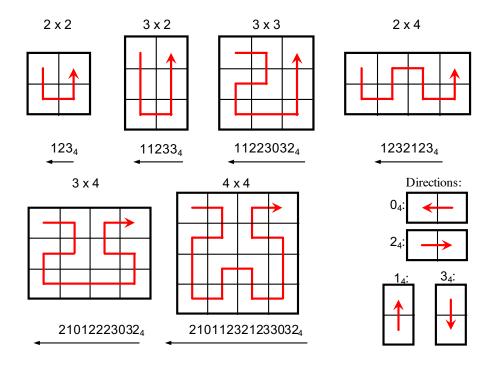

| 5.4 | Examples of Nano-programs for Grids Ranging from $2 \times 2$ to $4 \times 4$ (all having                                                                                                                                         | 02 |

| J.T | basic orientation $d=2$ )                                                                                                                                                                                                         | 58 |

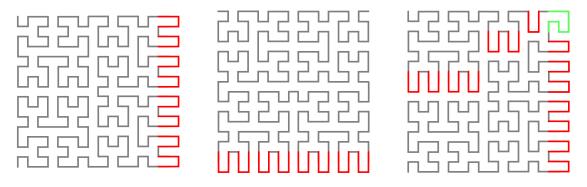

| 5.5 | Placement of $3 \times 2$ (red) and $3 \times 3$ (green) Grids                                                                                                                                                                    | 61 |

| 0.0 | i facement of $3 \times 2$ (red) and $3 \times 3$ (green) Girds                                                                                                                                                                   | 01 |

xiv LIST OF FIGURES

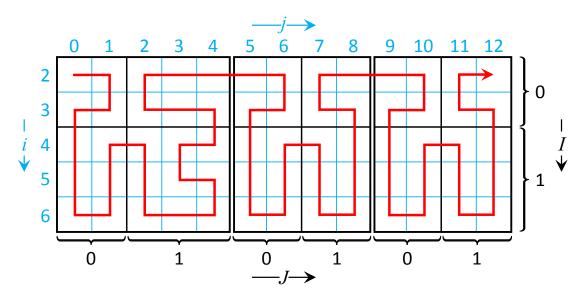

| 5.6  | FurHilbertFor $(i, j) \in \{2,, 6\} \times \{0,, 12\}$                              | 62  |

|------|-------------------------------------------------------------------------------------|-----|

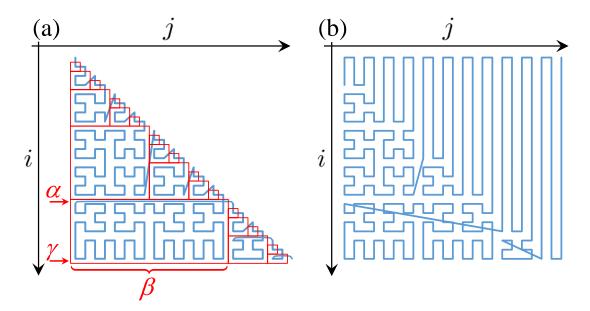

| 6.1  | Traversal of Cholesky (a) and Floyd/Warshall (b)                                    | 66  |

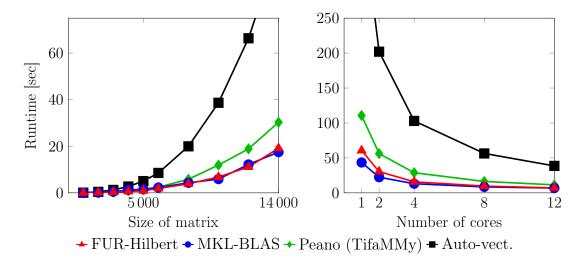

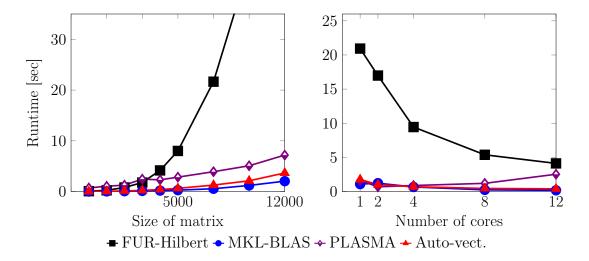

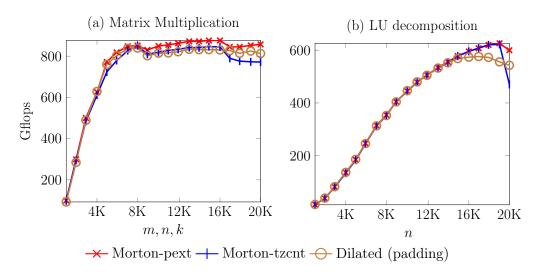

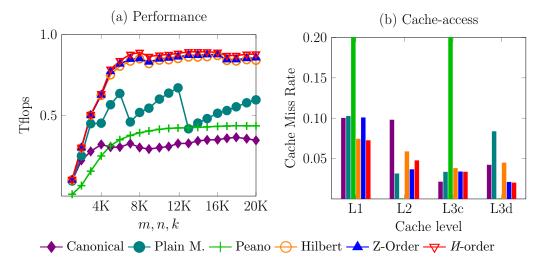

| 6.2  | Performance of Matrix Multiplication (Xeon)                                         | 69  |

| 6.3  | Performance of Matrix Multiplication on a Manycore System (Xeon Phi)                | 71  |

| 6.4  | Experiments on matrix multiplication for a smaller cache size (Laptop)              | 71  |

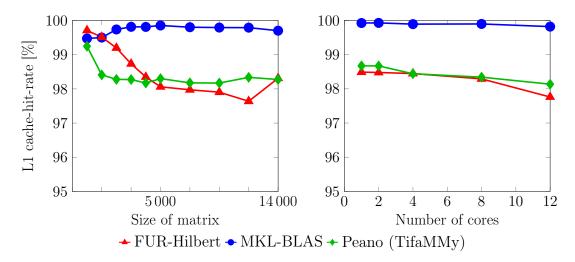

| 6.5  | Cache-hit-rate of the matrix multiplication on L1 cache for different matrix        |     |

|      | sizes (left) and different thread sizes (right)                                     | 72  |

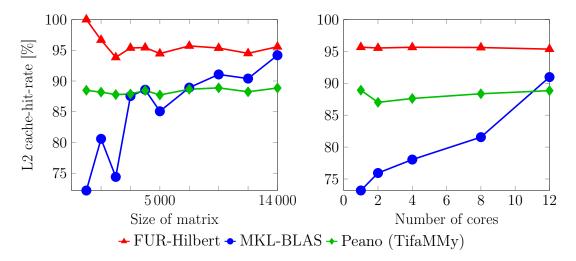

| 6.6  | Cache-hit-rate of the matrix multiplication on L2 cache for different matrix        |     |

|      | sizes (left) and different thread sizes (right)                                     | 73  |

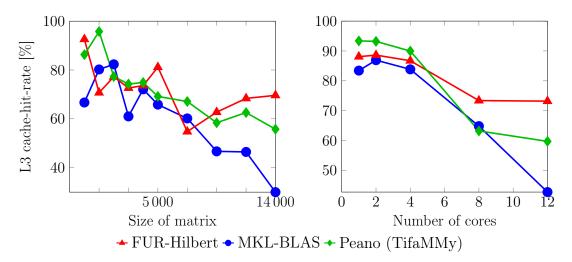

| 6.7  | Cache-hit-rate of the matrix multiplication on L3 cache for different matrix        |     |

|      | sizes (left) and different thread sizes (right)                                     | 73  |

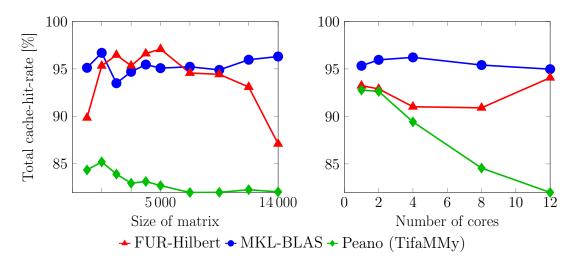

| 6.8  | Cache-hit-rate of the matrix multiplication along the complete cache hierarchy      |     |

|      | for different matrix sizes (left) and different thread sizes (right)                | 74  |

| 6.9  | Experiments on K-means Clustering                                                   | 75  |

| 6.10 | Experiments on Cholesky Decomposition                                               | 77  |

| 6.11 | Experiments on the Algorithm by Warshall                                            | 78  |

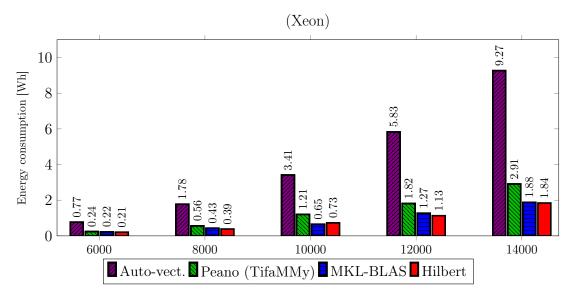

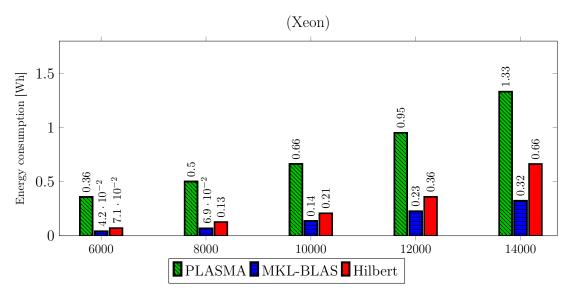

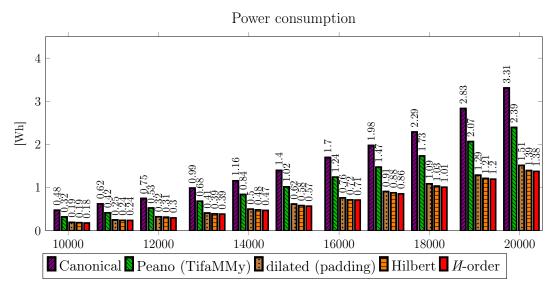

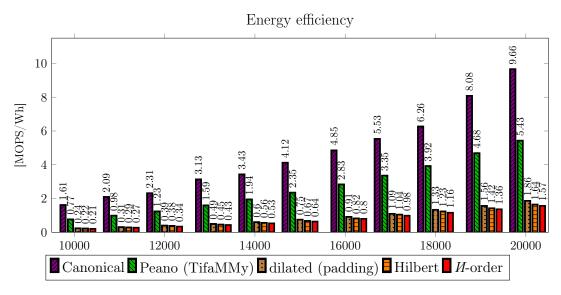

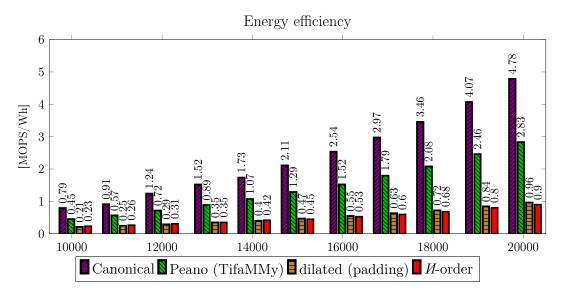

| 6.12 | Energy efficiency for matrix multiplication                                         | 78  |

| 6.13 | Energy efficiency for Cholesky decomposition                                        | 79  |

| 6.14 | Energy efficiency for K-means clustering                                            | 80  |

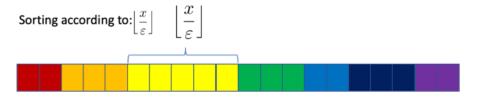

| 7.1  | Sorting of 20 vector objects in the Epsilon-Grid Order (EGO)                        | 86  |

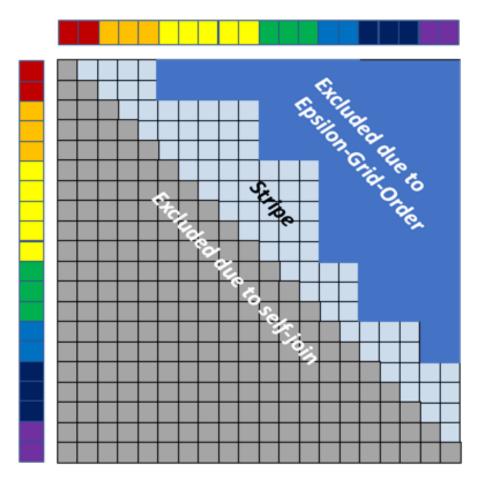

| 7.2  | Imaginary similarity matrix for the $\varepsilon$ -similarity join                  | 87  |

| 7.3  | Strategies to Process Pairs $(i, j)$ of Objects                                     | 90  |

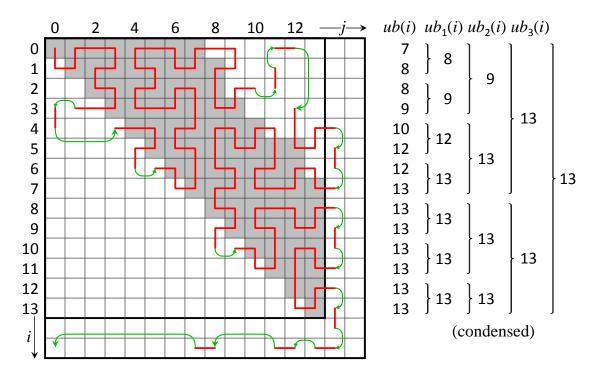

| 7.4  | EGO-Join using a FGF-Hilbert loop                                                   | 94  |

| 7.5  | Planning Refinements: Upper bounds of intervals (right side) are stored and         |     |

|      | condensed; thus larger areas of the $(i,j)$ -space can be efficiently discarded     |     |

|      | from loop traversal (left)                                                          | 98  |

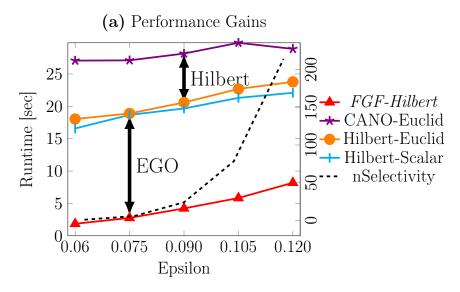

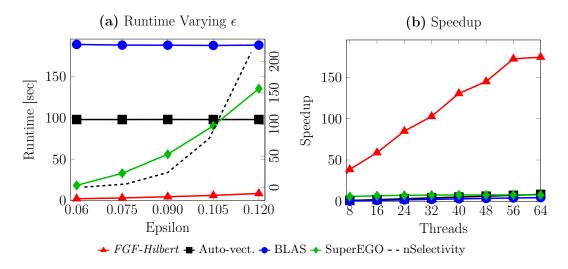

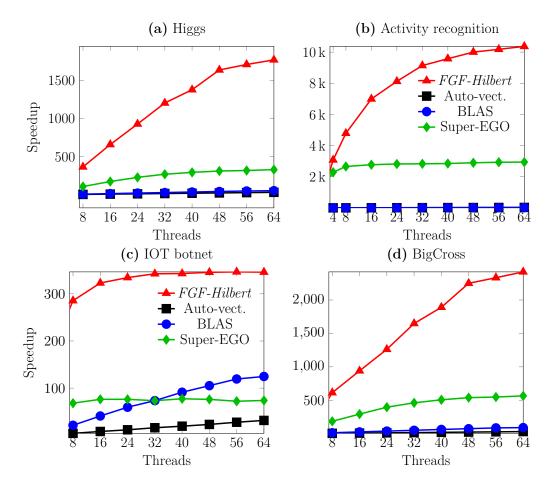

| 7.6  | The gain in performance of EGO and FGF-Hilbert Join                                 | .07 |

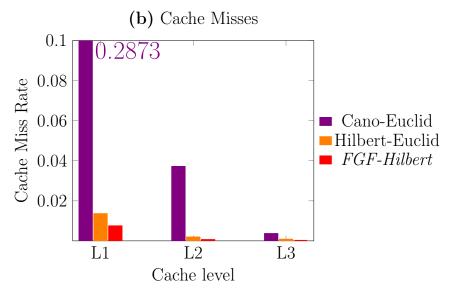

| 7.7  | Cache misses of Canonical, Hilbert and $\mathit{FGF-Hilbert\ Join} \ldots \ldots 1$ | .08 |

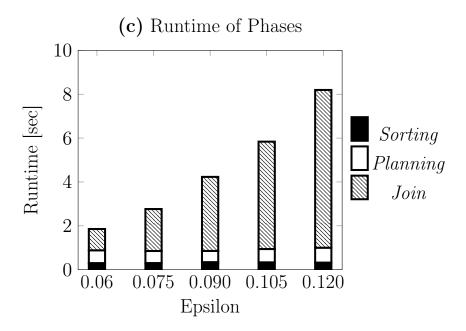

| 7.8  | Runtime of each phase in $FGF$ -Hilbert $Join$                                      | .09 |

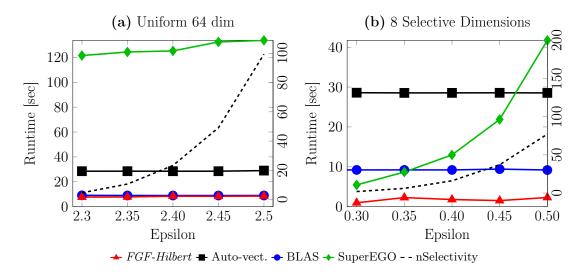

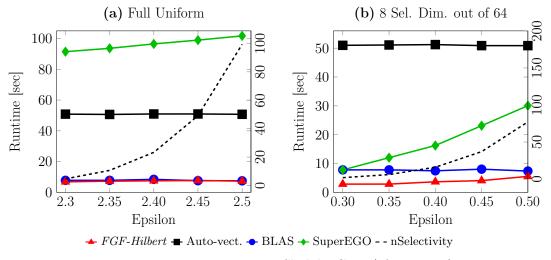

| 7.9  | (a) Full Uniform. (b) 8 Selective Dimensions and 56 Non-selective Dims.             |     |

|      | (Uniform, 200K, 64d)                                                                | .10 |

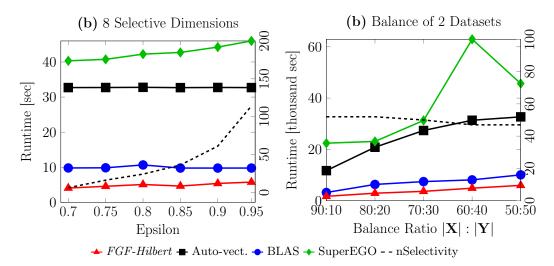

| 7.10 | `                                                                                   |     |

|      | form, $2 \cdot 200$ K, 64d)                                                         | .11 |

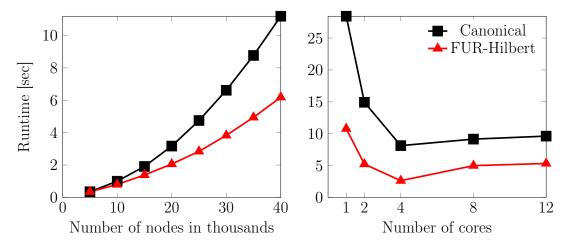

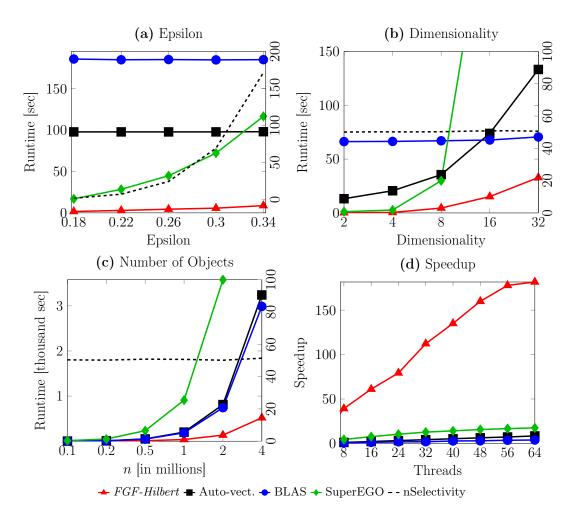

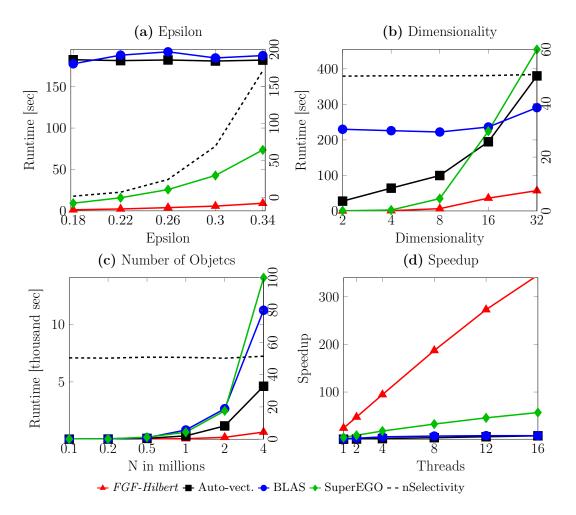

| 7.11 | Runtime Experiments (Default: Uniformly Distributed, 600K, 8d) 1                    | 12  |

LIST OF FIGURES xv

| 7.12 | Runtime Experiments on Gaussian Data (Gaussian, 600K, 8d) 113                                                        |

|------|----------------------------------------------------------------------------------------------------------------------|

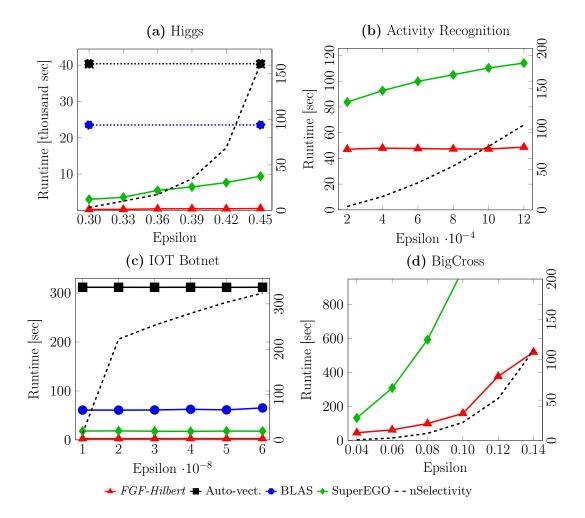

| 7.13 | Runtime Experiments on Real Data. Properties in Table 7.2                                                            |

| 7.14 | Experiments on Skylake CPU (cf. Fig. 7.9)                                                                            |

| 7.15 | Runtime Experiments on Skylake CPU (Default: Uniformly Distributed, 600K,                                            |

|      | 8d; cf. Figure 7.11)                                                                                                 |

| 7.16 | Speedup experiments on real data. Properties in Table 7.2 117                                                        |

| 8.1  | Strategies for space-filling curves, violations of monotonicity properties marked                                    |

|      | in red                                                                                                               |

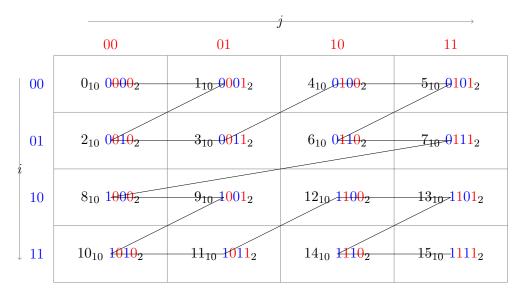

| 8.2  | Morton-order. Interleaving the binary coordinates from $i$ and $j$ yields the                                        |

|      | binary z-values shown                                                                                                |

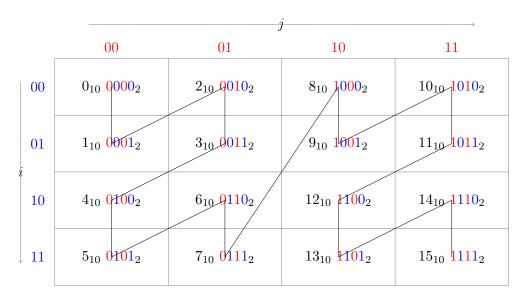

| 8.3  | U-order. Interleaving the binary coordinates from $i$ and $j$ yields the binary                                      |

|      | z-values shown                                                                                                       |

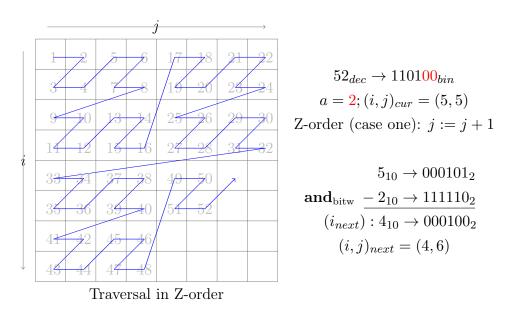

| 8.4  | Z-order traversal (tzcnt)                                                                                            |

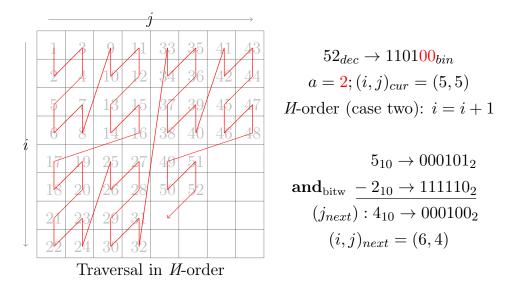

| 8.5  | <i>H</i> -order traversal (tzcnt)                                                                                    |

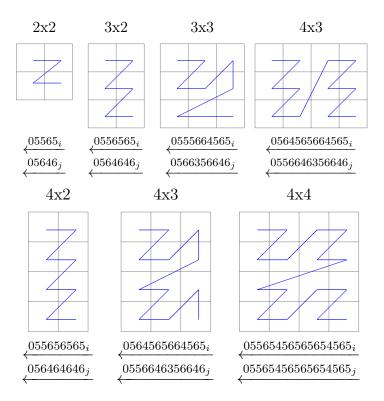

| 8.6  | Microcell templates                                                                                                  |

| 8.7  | Microcell placement of 5 $\{2 \times 3\}$ , 1 $\{3 \times 3\}$ , 5 $\{2 \times 4\}$ and 1 $\{3 \times 4\}$ templates |

|      | (c.f. Figure 8.6) into a 13x7 grid                                                                                   |

| 8.8  | SIMD parallelization                                                                                                 |

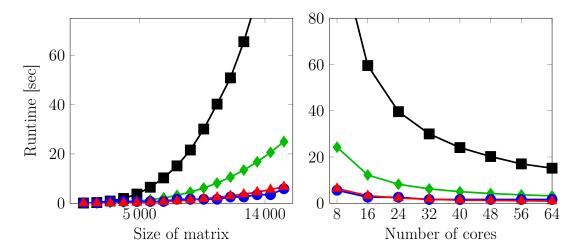

| 8.9  | Comparison of different Morton-order generation approaches (Xeon-Phi) 140                                            |

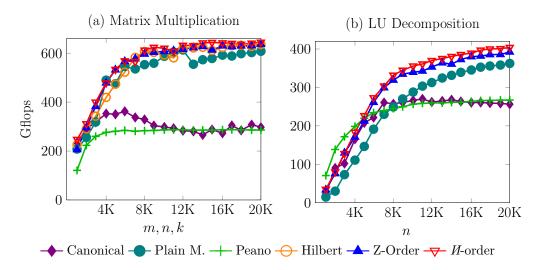

| 8.10 | Matrix-multiplication on Xeon-Phi                                                                                    |

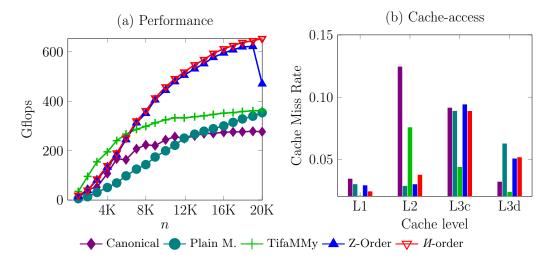

| 8.11 | LU decomposition on Xeon-Phi                                                                                         |

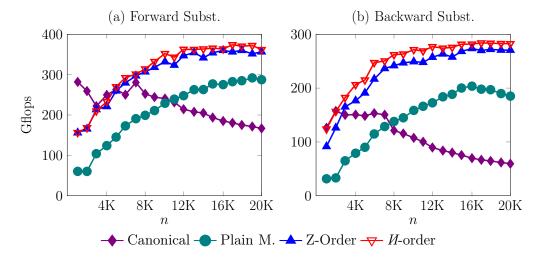

| 8.12 | Forward and backward substitution                                                                                    |

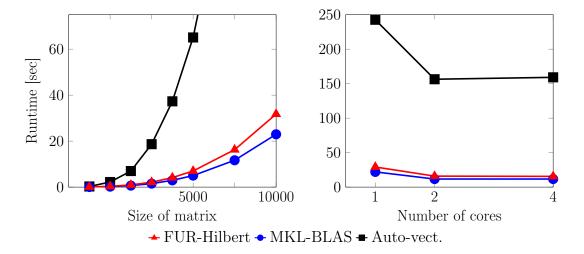

| 8.13 | Results evaluated on Xeon                                                                                            |

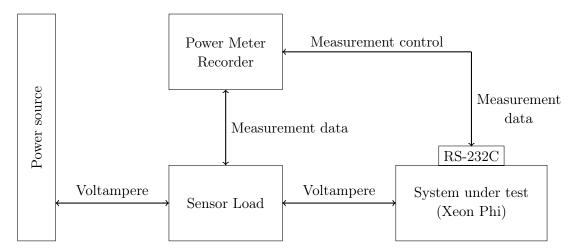

| 9.1  | Power meter set-up                                                                                                   |

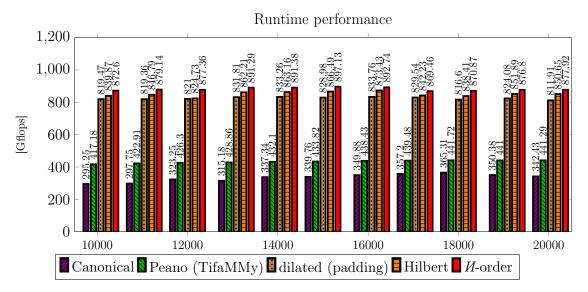

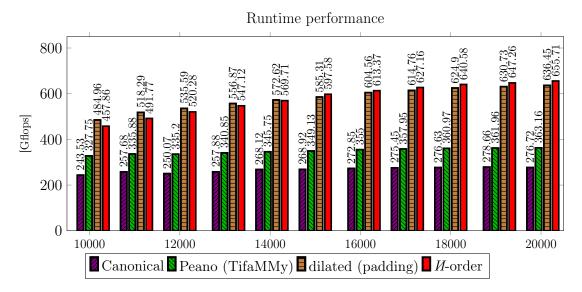

| 9.2  | Runtime performance of the matrix-multiplication on Xeon-Phi                                                         |

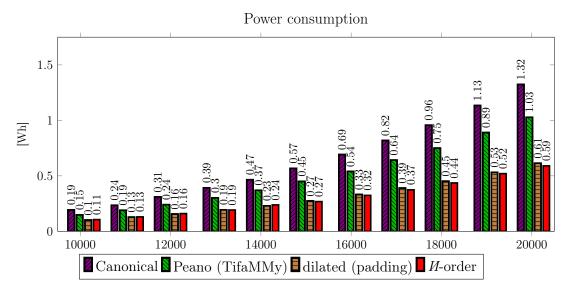

| 9.3  | Power consumption of the matrix-multiplication on Xeon-Phi                                                           |

| 9.4  | Energy efficiency of the Matrix-multiplication on Xeon-Phi                                                           |

| 9.5  | Runtime performance of the LU decomposition on Xeon-Phi 154                                                          |

| 9.6  | Power consumption of the LU decomposition on Xeon-Phi 154                                                            |

| 9.7  | Energy efficiency of the LU decomposition on Xeon-Phi                                                                |

| 10.1 | Interesting Space-Filling curves                                                                                     |

# List of Tables

| 5.1 | Lookup table to derive the direction code $d$ for the odd cases of $\ell$ 5  | 7 |

|-----|------------------------------------------------------------------------------|---|

| 5.2 | Lookup table to derive the direction code $d$ for the even cases of $\ell$ 5 | 8 |

| 7.1 | Properties of Synthetic Data                                                 | 5 |

| 7.2 | Properties of Real Data                                                      | 6 |

| 8.1 | Code table for processing microcells                                         | 9 |

| A.1 | Runtime on two different Morton order implementations tested on matrix       |   |

|     | multiplication                                                               | 5 |

| A.2 | Runtime on two different Morton order implementations tested on LU decom-    |   |

|     | position                                                                     | 6 |

# List of Algorithms

| 1  | Recursive Lindenmayer Algorithm               |

|----|-----------------------------------------------|

| 2  | The Non-recursive Lindenmayer Alg             |

| 3  | Lindenmayer with Nano-programs                |

| 4  | MORTON-ORDER (pext) loop                      |

| 5  | MORTON-ORDER (tzcnt) loop                     |

| 6  | Microcell placement with Morton-order (pext). |

|    | Implemented as a preprocessor macro           |

| 7  | LU block algorithm                            |

| 8  | Canonical LU decomposition                    |

| 9  | Backward substitution algorithm               |

| 10 | Forward substitution algorithm                |

| 11 | Matrix multiplication                         |

### Chapter 1

### Introduction

Multi-core processors are the standard microarchitecture of our everyday life. Multiple cores are prevalent in current desktop, workstations, notebooks, smartphones, tablets, NAS systems, or even embedded systems powered by ARM© processors (e.g., Raspberry Pi 4 equipped with 4-core ARM Cortex-A72). Until 2005, single core processors dominated the PC sector. Before that, attempts to increase performance by using two or more single-core processors were rarely made. Instead, the focus was on increasing the clock frequency in addition to new instruction sets such as MMX. Nevertheless, from frequencies of about 4 GHz on, the resulting heat dissipation was no longer manageable. One possibility for further development was the introduction of multi-core processors. The world's first dual-core processor was POWER4, a 1 GHz processor invented by IBM in 2001 [26], and it initiated the transition to multi-core systems. This has been the crucial development responding to the ever increasing demand for computing power [99]. By Multiple Instruction Multiple Data (MIMD) parallelism, multi-core systems maximize the amount of data that can be processed while keeping the clock speed and thus the energy consumption manageable.

Besides MIMD, Single Instruction Multiple Data (SIMD) parallelism or vectorization has been an important design principle going back to the Cray-1 supercomputer of 1976 [2]. In this parallelization principle, the same instruction is applied to many data streams, as in a vector processor. Modern microprocessors offer instruction sets for efficiently processing single instructions on multiple data. The most common are the instruction sets SSE (Streaming SIMD Extensions), AVX (Advanced Vector Extensions) and its latest extension to 512-bits AVX-512. For example, even smartphone processors, such as the ARM Cortex-A series of RISC processors, supports with NEON

an instruction set similar to SSE. The instruction sets operate on a reserved set of registers such that SIMD and the usual floating-point unit operations of the CPU core can be interleaved in the same clock cycle. Data within the registers reserved for SIMD (called YMM<sub>0</sub> to YMM<sub>32</sub> in AVX-512) can be very efficiently manipulated. For example, on the Skylake architecture with AVX-512, we have a vector length of 8 double-precision. Each core is equipped with 2 AVX-512 units, where each unit can perform a Fused-Multiply-Add (FMA) operation, which is an addition and one multiplication at the same time (dest = (a\*b) + c). Thus, this leads to 32 (= 8\*2\*2) double precision FLOPs per clock cycle. Compared to the previous Broadwell architecture, the processor speed has doubled, and the cache-hierarchy has significantly grown. However, the L2 cache latency has not improved, and there are only minor improvements in terms of latency for the L1 cache [66]. This known gap between processor speed and memory hierarchies remains, and similar characteristics apply to other common architectures. To scale up data mining methods on current architectures, we need to completely re-engineer algorithms with the opportunities provided by the hardware in mind.

To overcome this speed difference, caches are used to accelerate access to frequently used data. Thus, this demands an additional need to develop software algorithms that consider cache memory. A good part of the available performance cannot be used. The performance achieved by simple algorithms is very often relatively poor. There are various highly optimized libraries such as LAPACK [6], OpenBLAS [138] or the ATLAS project [128], but these implementations are based on hardware-tailored implementations and optimizations or at least automatically tuned for a given hardware, as in ATLAS. These libraries can be considered as **cache conscious algorithms**. They have hardware-related information such as cache-sizes (or the length of the cache lines) as an explicit parameter to exploit the memory hierarchy efficiently. One example for such hard-coded information is the step size in the matrix-matrix multiplication such as:

for

$$I:=0$$

to  $n-1$  stepsize  $s$  do

$$\text{for } j:=0 \text{ to } m-1 \text{ do}$$

$$\text{for } i:=I \text{ to } I+s-1 \text{ do } a_{i,j}:=\sum_k b_{i,k}\cdot c_{j,k}^{\mathsf{T}}$$

Assuming, that the L1 cache is large enough to store s rows of B and 1 row of  $C^T$ . This strategy improves the performance dramatically, because now we have to transfer  $C^T$  from main memory to cache only  $\lceil n/s \rceil$  times while we still transfer matrix B once. Cache-conscious approaches have such hard-coded information at multiple loop levels, where the step-sizes are tuned for each hardware and cache level respectively. In this example, we are using the transpose of C, since in C-like languages matrices are stored in a row-wise order and there it is common practice to transpose C before computing the scalar product.

Cache-oblivious algorithms [55] uses the cache optimally ignoring constant factors, such as cache sizes as an explicit parameter. Such an algorithm is designed to perform well on multiple machines with different memory hierarchies without modifications. Thus a cache-oblivious algorithm is designed to work well on multiple machines with different levels of the memory hierarchy of unknown sizes.

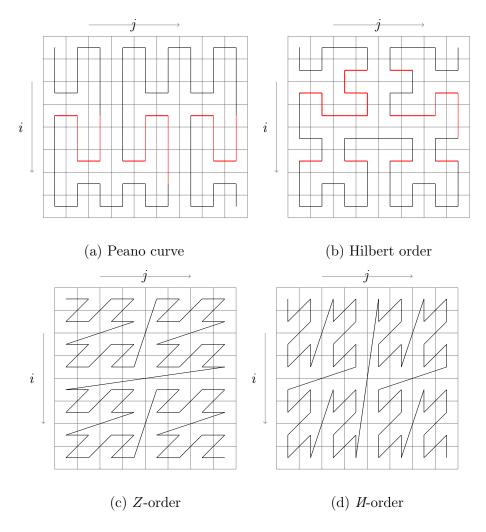

Figure 1.1: Strategies for space-filling curves.

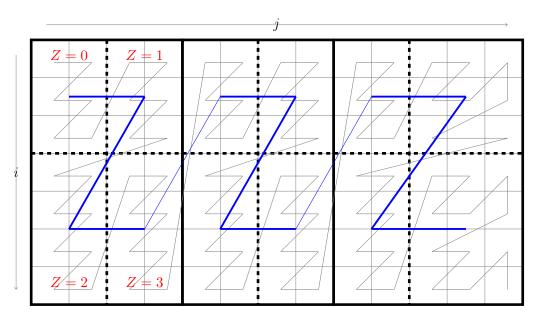

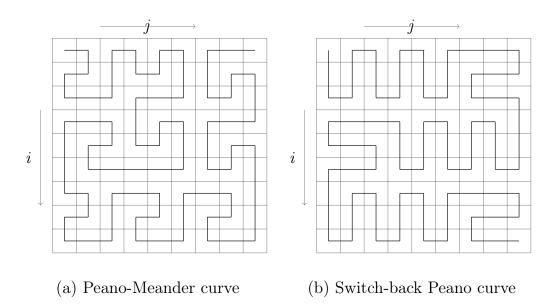

Typically, a cache-oblivious algorithm works by a recursive divide and conquer strategy. The problem is divided into smaller subproblems, where the size of the subproblem fits into the cache, regardless of its cache size. Instead of this recursive approach, in this thesis we define the size of our problem by a space-filling curve (cf. Figure 1.1), especially the Hilbert curve (1.1d), and the Morton-order curve (Figure 1.1c and e).

There are countless algorithms in various domains, such as graph traversal, clustering, or linear algebra. A nested loop structure is the core of these algorithms. The traversal of such loops over arrays or matrices are typically in canonical order, like Figure 1.1a, or in a block-oriented order such as Figure 1.1f. In this thesis, we propose to replace this nested loop structure with an order defined by a space-filling curve, which has the advantage of preserving the data locality and therefore, supporting today's rich memory hierarchy.

Modern hardware usually supports a memory hierarchy of 2-3 levels where this data locality property enables the benefits of cache-oblivious loops. With the cache-conscious approach, depicted in Figure 1.1f, we outline one prime example of a cache-conscious traversal. Here, we have to emphasize that each block (here  $4 \times 4$ ) might depend on the hardware used.

A space-filling curve is a curve in mathematical analysis, whose range contains the entire *n*-dimensional unit hypercube. In the context of scientific computing and throughout this thesis, we define a one-dimensional ordering of a two-dimensional space, such that each point or cell of the matrix is visited once. The aim is to conserve locality and bridge the gap between processor speed and the speed of memory access.

Space-filling curves have become a valuable tool in many scientific applications where locality in space is essential. The applications in scientific computing are versatile, but all the applications share a common sense of locality. In [111], the authors define a range query based on the Z-order and the Hilbert-curve. The latter is the subject of building up an index for image data [92]. There are also very general approaches of mapping points to space-filling curves [106], but in contrast to these approaches, we exploit the cache hierarchy by replacing the canonical loops with loops, which are defined by a space-filling curve.

### 1.1 Contributions

In this thesis, we present the following key contributions:

- We present Multi-Core K-means, a cache-conscious implementation for today's multi-core microarchitecture.

- We propose to replace nested loops enumerating pairs of (i,j) in canonical order

1.2. PUBLICATIONS

by **cache-oblivious loops** following a space-filling curve, especially the Hilbert-and the Morton-order curve.

5

- We overcome the usual limitation of space-filling curves to grids of equal size lengths  $n \times n$  where n is a power of 2 or 3.

- We implement our Hilbert- and Morton-order loops as a preprocessor macro, making it extremely convenient to be used as a building block in any host algorithm and facilitates compiler optimization.

- We demonstrate the superiority by applying our loops in several host algorithms, above all the matrix multiplication, which serves here compared to state-of-the-art approaches.

- We introduce the idea of using space-filling curves for the refinement order in a similarity join.

### 1.2 Publications

Parts of this Ph.D. thesis have been published and presented at international peerreviewed conferences and journals:

• Christian Böhm, Martin Perdacher, and Claudia Plant. 'Cache-oblivious loops based on a novel space-filling curve'. In: 2016 IEEE International Conference on Big Data, BigData 2016, Washington DC, USA, December 5-8, 2016. IEEE Computer Society, 2016, pp. 17–26.

- Christian Böhm, Martin Perdacher, and Claudia Plant. 'Multi-core K-means'. In: Proceedings of the 2017 SIAM International Conference on Data Mining, Houston, Texas, USA, April 27-29, 2017. Ed. by Nitesh V. Chawla and Wei Wang. SIAM, 2017, pp. 273–281.

- Christian Böhm, Martin Perdacher, and Claudia Plant. 'A Novel Hilbert Curve for Cache-locality Preserving Loops'. In: *IEEE Transactions on Big Data* (2018), pp. 1–14. ISSN: 2332-7790.

- Martin Perdacher, Claudia Plant, and Christian Böhm. 'Cache-oblivious High-performance Similarity Join'. In: Proceedings of the 2019 International Conference on Management of Data, SIGMOD Conference 2019, Amsterdam, The Netherlands, June 30 July 5, 2019. ACM, 2019, pp. 87–104.

- Martin Perdacher, Claudia Plant, and Christian Böhm. 'Improved Data Locality

Using Morton-order Curve on the Example of LU Decomposition'. In: 2020 IEEE

International Conference on Big Data, BigData 2020, Atlanta, GA, USA, December

10-13, 2020. Accepted for publication. Dec. 2020.

### 1.3 Structure of this Thesis

In this thesis, we focus on the shared memory architecture. The parallelism in such environments is briefly summarized in section 2. We look at MIMD and SIMD parallelization techniques and the memory hierarchy in particular. Chapter 3 we focuses on Multi-core processors and proposes a *cache-conscious* solution (c.f. Figure 1.1f) with today's common cache-hierarchy for the wide-spread clustering algorithm K-means as a highly relevant use-case for knowledge discovery on big data. We propose an entirely re-engineered clustering algorithm focusing on the close connection of the MIMD and SIMD parallelism. However, we observed that the code needs significant changes if we migrate the code to a different hardware setting. Some step-sizes related to the memory hierarchy need fine-tuning to tease out the performance last percentage. We address this issue by rewriting the loops in an order defined by a space-filling curve. Therefore we deal with *cache-oblivious* algorithms in the upcoming chapters. Before diving into space-filling curves and how they are applied in this thesis, we introduce the basic terminology and observations from previous publications in this field in chapter 4.

In chapter 5 we propose to replace nested loops in algorithms with a loop defined by the Hilbert curve (c.f. Figure 1.1d). We revisit well-known methods for generating the Hilbert curve and propose our non-recursive solution for arbitrarily shaped rectangles. On top of our Hilbert curve, we implemented several algorithms, such as the matrix-multiplication, K-means clustering, Cholesky decomposition, and Floyd's algorithm to find the shortest paths of all pairs in a graph. The implementation details and extensive experiments are summarized in chapter 6.

In chapter 7, we have a detailed look at shared-memory databases, where we apply the Hilbert curve to the  $\varepsilon$ -similarity join. In particular, we sort the data according to the Epsilon Grid Order (EGO), which serves here as a filter technique. We traverse the remaining part of the non-materialized similarity matrix in a Hilbert-order. In the experiments, we show our technique's various building blocks' impact and demonstrate its use on various synthetic and real-world data sets.

There are use cases where the Hilbert-curve is not applicable because of certain algorithms' data dependencies. LU decomposition is one example. In chapter 8 we introduce our contribution to the Morton-order curve for two different variants, the Z-order and the *M*-order (c.f. Figure 1.1c and e) an inverse version of the Z-order. Extensive experiments on the LU decomposition, matrix-multiplication, and forward- and backward substitution show their superiority over the Hilbert curve.

Space-filling curves like the Hilbert curve or the Morton-order curve reduce the cache misses, and therefore they have an improved data movement pattern. Since data movement is expensive in terms of energy efficiency, it is worth having a look at energy consumption in chapter 9. We measure energy efficiency with an external wattmeter between the power supply and the server to have an undistorted result.

We conclude our thesis in chapter 10 and give some outline on possible future research.

### Chapter 2

# Parallelism in Shared Memory Environment

In this chapter, we give a high-level introduction to different parallelism levels of shared memory environments. In section 2.1 we introduce into the MIMD and SIMD parallelism, the two most important principles, which are explicitly targeted in our work. In this chapter, we refer to other parallelism techniques such as instruction-level parallelism in section 2.2 or hardware multithreading in section 2.3, but we do not target these techniques directly within this thesis. We conclude this chapter with general remarks in section 2.4.

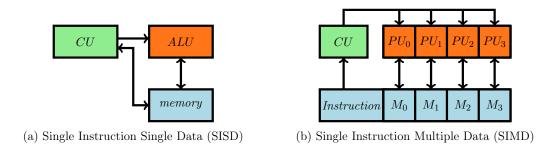

### 2.1 SIMD and MIMD

Flynn's taxonomy is a classification of computer architectures proposed in 1966 [53]. This taxonomy has been used as a tool in the design of modern processors and their functionality [48]. Flynn's four classifications are based on the number of concurrent instruction and data streams available in the architecture. The term "stream" refers to a sequence or flow of either instructions or data from the CPU's main memory. The instruction stream is unidirectional, and the data stream is bidirectional. The four-letter abbreviations SISD, SIMD, MISD, and MIMD were derived from the English descriptions' first letters. For example, SISD stands for "Single Instruction stream, Single Data stream". According to Flynn, SISD is a sequential computer with no parallelism in either instruction or data streams, like Intel<sup>©</sup> Pentium 4. There we have a Control Unit, which takes instructions from memory, which get forwarded to the Arithmetic-Logic Unit (ALU). In Figure 2.1a

Figure 2.1: SISD and SIMD paradigm.

we visualized the information flow.

All input data are transferred via the ALU's main memory for processing and then written back to memory. Instead of doing this for only one memory cell, this can be done for a whole vector of data. This principle is known as "Single Instruction stream Multiple Data streams" (SIMD) and is nowadays implemented in embedded systems powered by ARM<sup>©</sup> with the NEON instruction set or in today's laptops as AVX2 or AVX-512 instruction set, c.f., Figure 2.1b. These instructions operate on multiple data elements simultaneously that make the processing of loops more efficient. The programmer does not need to take care of such SIMD instructions because they are generated automatically by the compiler with auto-vectorization. A vectorizing compiler transforms loops into sequences of vector operands. However, if the loop has a complex structure defined by macros, the automatic vectorization fails most of the time. Since we replace canonical loops in algorithms with loops defined by a space-filling curve, it is rarely the case to successfully vectorize such loops. Therefore, we use AVX-512 intrinsics instructions in this thesis directly. These are C style functions that provide access to many instructions, including Intel<sup>©</sup> SSE, AVX, or AVX-512, without the need to write assembly code. Writing code with such intrinsic instructions simulates the behavior of having an implemented auto-vectorized approach. Nevertheless, we believe that future compilers will profit from the locality assumptions of the Hilbert curve.

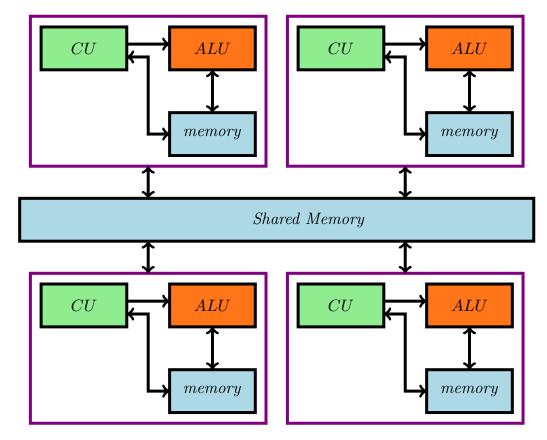

The Multiple Instruction stream on Single Data stream (MISD) is an untypical architecture that is generally used for fault tolerance systems, such as a space-shuttle flight control computer [57]. Multiple autonomous processors simultaneously executing different instructions on different data in the Multiple Instruction stream Multiple Data streams (MIMD) paradigm (c.f. Figure 2.2). MIMD architectures include multi-core processors and distributed systems, using either a shared or a distributed memory space.

Figure 2.2: MIMD paradigm.

Most parallel computers, as of 2013, are MIMD systems. An example of a MIMD system is the Intel<sup>©</sup> Xeon Phi<sup>™</sup>. This processor has multiple processing cores (up to 72 in 2017) to execute different instructions on different data. However, distributed systems with distributed memory environments like a hypercube or mesh interconnection network are also considered MIMD parallel systems. However, throughout the context of this thesis, we focus explicitly on shared memory environments where we refer with the term MIMD parallelism to threading parallelism in multi- or many-core environments. In such multi- and many-core environments, both SIMD and MIMD are combined to achieve maximum performance.

### 2.2 Parallelism via Instructions

Since about 1985, all processors use pipelining to overlap the execution of instructions and improve the performance. Such a potential overlap among instructions is called

instruction-level parallelism (ILP). As a simple example, considering that reading from memory has a higher latency than performing the actual computation. This effect would cause the CPU to stall. In the meantime, the CPU could decrease a pointer if the mentioned computation does not depend on this pointer. The primary goal is to do some productive work instead of stalling for higher latency operations.

We address this issue by loop unrolling, where multiple copies of the loop body are made. After unrolling, there is more ILP available by overlapping instructions from different iterations. The compiler has then more options to address the ILP.

### 2.3 Hardware Multithreading

A related concept to MIMD, especially from a programmer perspective, is hardware multithreading. While MIMD relies on multiple processes or threads to keep multiple processors busy, hardware multithreading allows multiple threads to share the functional units of a single processor in an overlapping fashion to utilize the hardware resources efficiently. Multithreaded processors, therefore, process several threads quasi-simultaneously. This kind of parallelism can be done in different ways:

- Fine-grained multithreading: A version of hardware multithreading that switches between threads on each instruction. This technique allows each core an interleaved execution of threads. The main goal is to avoid delays or stalls in the instruction stream (=instruction pipeline). These can occur if a thread reads after it writes, and the instruction refers to a result that has not yet been calculated or retrieved.

- Coarse-grained multithreading: This type of multithreading occurs if a thread gets blocked by an event (e.g., L3 cache miss) that typically would create a long latency stall. While this stall might take hundreds of CPU cycles, the threaded processor switches the execution to another thread that is ready to run. The stalled thread is set to ready-to-run after the data arrives.

- Simultaneous multithreading (SMT): Any single thread has a limited amount of ILP. This multithreading type tries to exploit the ILP parallelism across multiple threads to decrease the stall time associated with unused issue slots. This can be done without major changes to the processor architecture: the main additions needed are the ability to fetch instructions from multiple threads and a larger register file to hold data from multiple threads. Often there are four concurrent

threads (or hyper-threads according to the Intel terminology) per CPU core, but some processors support even up to eight concurrent threads per core.

Exploiting these levels of parallelism is far beyond the scope of our thesis. In our experiments, we do not address fine- or coarse-grained multithreading or hyper-threading explicitly. In all of the mentioned cases above, we rely on default compiler optimizations. We test the performance of our algorithms always with one thread per core.

### 2.4 General Remarks

There are even more opportunities in a shared memory environment to address performance issues explicitly. One example is how processors can access the address space. There are two different styles, the Uniform Memory Access (UMA) and the NonUniform Memory Access (NUMA). In the UMA style, the latency to a word in the memory does not depend on which processor asks for it. In the NUMA style, memory accesses to the High Bandwidth Memory (HBM) are much faster than others, depending on which processor asks which word, typically because the main memory is divided and attached to different microprocessors or different memory controllers on the same chip. However, to take advantage of this architecture, the developer must make the application NUMA-aware. Developers using OpenMP can do so using nested parallelism in OpenMP, where the so-called teams bind to NUMA nodes, and threads in a team use the processors within one NUMA node.

In the case of one of our servers, the Intel<sup>©</sup> Xeon Phi<sup>™</sup>, which comes with additional on-package HBM. The HBM can be used as an L3 cache or as a fast addressable memory or in a hybrid model, where half of the memory is used as cache and the other half as fast addressable memory.

Since we want to guarantee fair comparisons, we decided to use the HBM entirely as a third level cache. Furthermore, we do not rely on explicit programming techniques to bind threads to specific NUMA nodes. Our way of programming guarantees fairness to comparison partners. We rely on the default hardware and compiler settings for other concepts, such as speculation or cache-coherence.

## Chapter 3

# Multi-core K-means

### 3.1 Introduction to a Cache-conscious Approach

To scale up data mining methods on current architectures, we need to re-engineer algorithms with the current hardware capabilities in mind entirely. As a showcase, we consider K-means clustering in a shared memory environment, such as current workstations or laptops. The main memory of current systems is usually large enough to occupy millions of data points. Therefore, we do not assume disk accesses. Parallel variants of K-means for distributed (shared-nothing) environments have been proposed [63, 135] and can be combined with our approach. We focus on exploiting MIMD and SIMD parallelism while optimally feeding each core with data along the memory hierarchy from registers to various cache levels. At first glance, this might seem an easy task since standards like Open-MP support MIMD parallelism, and SIMD parallelism is enabled by auto-vectorization performed by common compilers like GNU C++. However, if the algorithm's logical flow is not tailored to the opportunities and limitations of current architectures, we cannot expect significant performance gains.

In section 3.2, we revisit the K-means algorithm to fix the notation and outline the canonical implementation of the algorithm. We combine the canonical K-means algorithm with MIMD and SIMD parallelization techniques, including efficient use of available registers, outlined in section 3.3. We propose an elegant way to avoid branching in section 3.4, where we code current cluster memberships already in the data points. In our experiments, we compare the auto-vectorized technique and a K-means implementation based on Intel<sup>©</sup> BLAS [47] a quasi-standard for linear algebra operations in shared memory environments. In section 3.7 we give some concluding remarks.

### 3.2 K-means

To make this chapter self-contained, we introduce here the K-means algorithm for clustering n data points  $x_0, ..., x_{n-1}$  from a d-dimensional vector space. Throughout this chapter, we will use the notation  $x_i[\ell]$  for the  $\ell$ -dimension  $(0 \le \ell < d)$  of data point  $x_i$  and  $x_i[\ell, ..., \ell + 3]$  for a sub-vector. The algorithm starts with random initialization of the cluster representatives  $\mu_1, ..., \mu_k$  by k randomly selected points from the data set. Then, it repeats two steps until convergence: (1) assignment step: Each point  $x_i \in \mathbb{R}^d$  from the data set is assigned to that cluster j which minimizes the Euclidean distance  $||x_i - \mu_j||$ , and (2) re-determination of the cluster centers: each cluster representative is computed as the center of mass of the associated points (centroid). Often, the collection of sufficient statistics (count and sum) for the re-determination step is already integrated with the assignment step. Thus, K-means is canonically implemented by four nested loops:

```

while not converged

```

```

\begin{aligned} & \textbf{for } i := 0 \textbf{ to } n{-}1 & \leftarrow \text{consider } x_i \\ & \textbf{for } j := 0 \textbf{ to } k{-}1 & \leftarrow \text{compare it to } \mu_j \\ & \textbf{for } \ell := 0 \textbf{ to } d{-}1 & \leftarrow \text{Euclidean dist. } ||x_i - \mu_j|| \end{aligned}

```

The  $\ell$ -loop determines the Euclidean distance  $||x_i - \mu_j||$ . The j-loop determines the minimum among these distances, i.e.  $\min_{0 \le j < k} ||x_i - \mu_j||$  and additionally updates the sufficient statistics. A larger part of this chapter is devoted to changing this order of loop traversals to improve the transfer of information between main memory, cache, and registers.

### 3.3 Multi-core K-means

The main idea to parallelize our algorithm MKM (Multi-core K-means) is to enable MIMD parallelism at the level of data objects and SIMD parallelism at the level of dimensions. We distribute different contiguous subsets of the data objects to different threads running on different cores. We assign different dimensions of single objects and cluster representatives to different arithmetic/logic units within a core. For the implementation of MKM, we rely on Open-MP for MIMD and AVX1 for SIMD parallelism. For clarity, we base the following description on the common Ivy Bridge Processor Architecture characteristics with 16 registers of 256-bit size (4 double-precision floating-point vectors). However, the algorithm can easily be adapted to other micro-architectures.

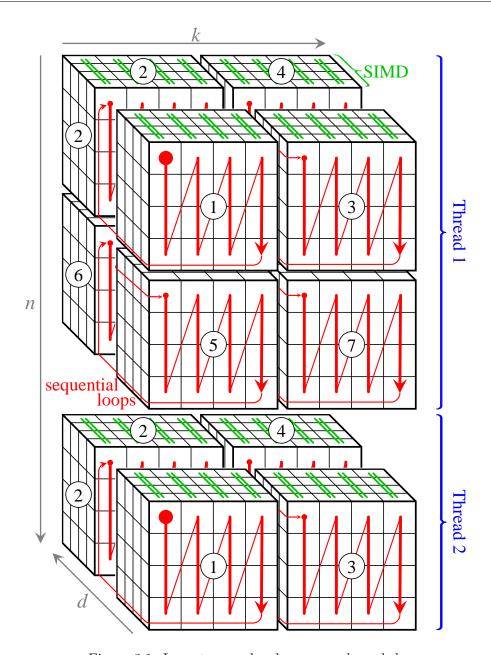

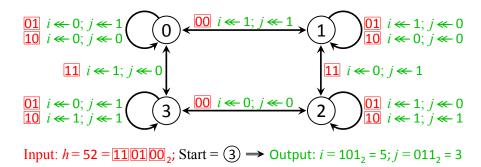

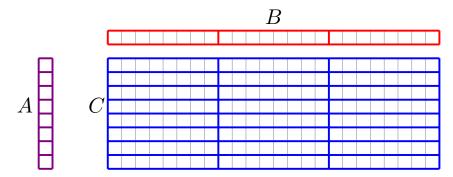

Figure 3.1: Loop traversal order over n, k, and d.

### MIMD-parallelism

Our algorithm multi-core K-means assigns different parts of the data set to the different threads, i.e., contiguous blocks of objects are assigned and processed by the same core. If several c cores are available, we divide the data set into c, almost equally sized subsets. For reasons discussed in the next section, we take care that each subset contains a number

of objects divisible by four (and the last subset is enlarged by up to 3 vectors  $[\infty, ..., \infty]$ ). If t is the thread number  $(0 \le t < c)$ , the start offset of the corresponding data subset is determined by  $4 \cdot \left\lceil \frac{n \cdot t}{4 \cdot c} \right\rceil$ . Additionally, each data vector is zero-padded to ensure that the data space's dimension is divisible by 4.

The easiest way of programming MIMD parallelism for multi-core processors is standards like Open-MP and CILK, where (among other possibilities) we have a special for-loop enabling parallel threads. In Open-MP, a usual for-loop in C-language syntax is prefixed by a compiler-hint ("#pragma omp parallel for"). Instead of executing a sequential loop, parallel threads are spawned (the number of which can be predefined by the user). Such loops have limitations, e.g., the loop iterator variable must not be modified in the loop body. Synchronization of memory access operations in the case of write dependencies is supported by critical sections (like "#pragma omp critical").

We use an Open-MP for-loop to parallelize the assignment step, which also collects the necessary statistics (sum and count of all assigned vectors) for K-means' next iteration. After this modified, MIMD-parallel assignment step, the threads are synchronized again, and a very efficient re-determination step computes from the collected statistics the new cluster representatives (centroids). MIMD parallelization of this re-determination (which is in  $O(d \cdot k)$  time, constant in n) does not pay off, but SIMD parallelism can be used, as described later.

We avoid entirely write dependencies by ensuring that each thread writes only to private variables. During the run of the K-means algorithm, we have two types of write operations: (1) the cluster IDs as the intermediate result of the assignment step, and (2) the collection of the statistics (sum and count of all assigned vectors) for the next K-means iteration. Since we assign blocks of contiguous objects to each thread, we implicitly assign a block of contiguous cluster-IDs to each thread, and therefore, we have no write conflicts in (1). The collection of statistics (2) is done in private variables for each thread, which causes a small memory overhead of  $O(d \cdot k \cdot c)$  and the same time complexity for the (non-parallel) consolidation of the private variables into global variables.

#### Efficient Use of SIMD Registers.

AVX1 offers us a relatively high number of 16 registers (called YMM<sub>0</sub> to YMM<sub>15</sub>) for SIMD operations, each of which can store up to 4 double-precision floating-point numbers (64 values in total). For high performance, it is essential to minimize data transfer from

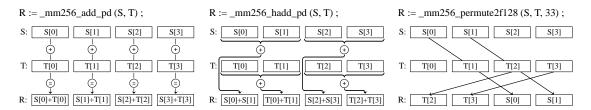

Figure 3.2: Vertical and Horizontal Addition, Permutation of Vectors.

and to these registers. As we want to avoid any restrictions on n, k,, and d, we cannot safely assume that whole points or centroids fit into the registers. Therefore, our strategy uses many of the registers (YMM<sub>0</sub> to YMM<sub>7</sub>) to store the intermediate results of 16 distance calculations between four data points (now called the *current points*) and four *current centroids*, respectively. Although it might seem sufficient to use four registers to store these 16 values, we will discuss later a performance issue why we use two variables for each distance, marked by "a" and "b". Moreover, we use five registers, each of which stores four subsequent dimensions of the current data points and the current centroids. We need two further registers for intermediate results and one register (YMM<sub>15</sub>) for the final minimal distances used in the assignment operation of the four current points. The following table gives us an overview, where  $x_0, ..., x_3$  are the four current points and  $\mu_0, ..., \mu_3$  are the four current centroids (actually standing for  $x_i, ..., x_{i+3}, \mu_j, ..., \mu_{j+3}$ ), and  $\ell, ..., \ell + 3$  are the four current dimensions:

$$\begin{split} & \text{YMM}_0 = \left[ ||x_0 - \mu_0||_{\mathbf{a}}^2, ||x_1 - \mu_0||_{\mathbf{a}}^2, ||x_0 - \mu_0||_{\mathbf{b}}^2, ||x_1 - \mu_0||_{\mathbf{b}}^2 \right] \\ & \text{YMM}_1 = \left[ ||x_2 - \mu_0||_{\mathbf{a}}^2, ||x_3 - \mu_0||_{\mathbf{a}}^2, ||x_2 - \mu_0||_{\mathbf{b}}^2, ||x_3 - \mu_0||_{\mathbf{b}}^2 \right] \\ & \text{YMM}_2 = \left[ ||x_0 - \mu_1||_{\mathbf{a}}^2, ||x_1 - \mu_1||_{\mathbf{a}}^2, ||x_0 - \mu_1||_{\mathbf{b}}^2, ||x_1 - \mu_1||_{\mathbf{b}}^2 \right] \\ & \vdots \\ & \text{YMM}_7 = \left[ ||x_2 - \mu_3||_{\mathbf{a}}^2, ||x_3 - \mu_3||_{\mathbf{a}}^2, ||x_2 - \mu_3||_{\mathbf{b}}^2, ||x_3 - \mu_3||_{\mathbf{b}}^2 \right] \\ & \text{YMM}_8, ..., \text{YMM}_{11} = x_0, ..., x_3 \text{ (current 4 dimensions)} \\ & \text{YMM}_{12} = \mu_0, \text{ later: } \mu_1, \mu_2, \mu_3 \text{ (current 4 dimensions)} \\ & \text{YMM}_{13}, \text{YMM}_{14}: \text{ reserved for intermediate results.} \\ & \text{YMM}_{15} = \left[ \min_j ||x_0 - \mu_j||, ..., \min_j ||x_3 - \mu_j|| \right] \end{split}$$

Using this storage scheme, we can efficiently make use of all 16 available SIMD registers. For this purpose, we have now to change our original loop scheme of K-means involving four loops into a new one involving eight loops, of which one (marked in blue) is an Open-MP loop operating MIMD parallel threads rather than sequential iterations. The

innermost (green) loop performs SIMD-parallel operations (multiply and add), and two other innermost loops (iterating over I and J) are not implemented as loops. However, they are instead explicitly programmed in an unrolled way in the C-language source code and in the following pseudo-code. The full hierarchy of 8 loops exactly represents how data objects and cluster representatives are accessed and processed. This order is also visually depicted in Figure 3.1, where the colors are consistent with the text colors in our eight loops: the green connected parts are simultaneously processed using SIMD parallelism, and the two simultaneous threads of MIMD parallelism are braced together in blue:

### while not converged

```

\begin{array}{lll} \mathbf{parallel} \ \mathbf{threads} \ \mathbf{for} \ t := 0 \ \mathbf{to} \ c - 1 & \leftarrow \mathbf{MIMD} \\ \mathbf{for} \ i := 4 \left \lceil \frac{nt}{4c} \right \rceil \ \mathbf{to} \ 4 \left \lceil \frac{n(t+1)}{4c} \right \rceil - 1 \ \mathbf{step} \ 4 \\ \mathbf{for} \ j := 0 \ \mathbf{to} \ k - 1 \ \mathbf{step} \ 4 \\ \mathbf{for} \ \ell := 0 \ \mathbf{to} \ d - 1 \ \mathbf{step} \ 4 \\ \mathbf{for} \ I := j \ \mathbf{to} \ j + 3 & \leftarrow \mathbf{unrolled} \\ \mathbf{for} \ I := i \ \mathbf{to} \ i + 3 & \leftarrow \mathbf{unrolled} \\ \mathbf{for} \ L := \ell \ \mathbf{to} \ \ell + 3 & \leftarrow \mathbf{SIMD} \end{array}

```

In Figure 3.1, each of the cubic blocks represents the processing of four current points and four current centroids in four current dimensions (three innermost loops). Note that the four current dimensions are processed by SIMD parallelism. The traversal pattern within each cubic block is generated by the two unrolled loops (J, I). The traversal order across blocks is established by the three loops i, j, and  $\ell$  (additionally marked by numbers).

The assembler instructions to process information in SIMD-registers have been mapped to higher programming languages like C. "Intrinsic operations" like  $_{\rm mm256\_add\_pd}$  and  $_{\rm mm256\_mul\_pd}$  often use two SIMD registers as operands and store the result in a third register, as demonstrated for the "add"-operation on the left side of Figure 3.2 where R, S, and T are any of the registers  ${\rm YMM}_{0,...,15}$ , and R[0],...,R[3] denote the 4 dimensions.

We can jointly load four subsequent values of  $x_i$  and  $\mu_j$  into registers, add, and multiply them for the Euclidean distance. However, the horizontal sum (the sum of several components *inside* a register) of these four intermediate results, which is finally needed for the Euclidean distance, is a bit more tricky. AVX offers an operation called "hadd"

(horizontal add), which can add only the first two and the last two vector components, respectively, for two source registers (cf. Figure 3.2, center).

The horizontal sum between the second and third component (e.g.) requires operations like blend and permute (Fig. 3.2 right side), causes more effort and is thus not done in the innermost loop (see later). It is better to defer this operation and to store instead of the two partial sums in independent components of the registers, although we are thus wasting 4 of the valuable registers. The three innermost of our eight loops are implemented in an unrolled way as follows (the indices in red color represent the unrolled loops (I, J, L) and help to figure out modifications in the three repeats of the sequence (\*)):

```

for \ell := 0 to d-1 step 4

YMM_8 := x_{i+0}[\ell, ..., \ell+3];

: likewise YMM<sub>9,...,11</sub> := x_{i+1,...,3}[\ell,...,\ell+3];

YMM_{12} := \mu_{i+0}[\ell, ..., \ell+3];

YMM_{13} := _mm256_mul_pd(YMM_8, YMM_{12});

YMM_{14} := mm256 \text{ mul } pd(YMM_9, YMM_{12});

YMM_{13} := _mm256\_hadd\_pd(YMM_{13}, YMM_{14});

YMM_0 := mm256 \text{ add } pd(YMM_0, YMM_{13});

YMM_{13} := _mm256 _mul _pd(YMM_{10}, YMM_{12});

YMM_{14} := mm256 \text{ mul } pd(YMM_{11}, YMM_{12});

YMM_{13} := \underline{mm256}\underline{hadd}\underline{pd}(YMM_{13}, YMM_{14});

YMM_1 := mm256 \text{ add } pd(YMM_1, YMM_{13});

(*) is 3 \times repeated with following modifications:

: \text{YMM}_{12} := \mu_{j+1}[\ell, ..., \ell+3]; \text{ add to YMM}_{2 \text{ and } 3};

: \text{YMM}_{12} := \mu_{j+2}[\ell, ..., \ell+3]; \text{ add to YMM}_{4 \text{ and } 5};

: YMM_{12} := \mu_{j+3}[\ell, ..., \ell+3]; \text{ add to } YMM_{6 \text{ and } 7};

```

Altogether, we have a number  $4 \cdot \lceil \frac{d}{4} \rceil$  of load operations for centroids (from L1-cache),  $4 \cdot \lceil \frac{d}{4} \rceil$  of load operations for data points (from main memory),  $16 \cdot \lceil \frac{d}{4} \rceil$  AVX-multiplications,  $8 \cdot \lceil \frac{d}{4} \rceil$  additions, and  $8 \cdot \lceil \frac{d}{4} \rceil$  "hadd"-operations. After finishing this  $\ell$ -loop our registers YMM<sub>0,...,7</sub> contain the 16 scalar products of the four current points  $x_i, ... x_{i+3}$  with the four current centroids  $\mu_j, ..., \mu_{j+3}$ . The horizontal sums must then be completed, and the scalar products must be changed into Euclidean distances using the following operations:

```

YMM_{13} := __mm256\_blend\_pd(YMM_0, YMM_1, 12);

YMM_{14} := __mm256\_permute2f128(YMM_0, YMM_1, 33);

YMM_{14} := __mm256\_add\_pd(YMM_{13}, YMM_{14});

YMM_{13} := __mm256\_broadcast\_sd(scalar[j+0]);

YMM_{13} := __mm256\_sub\_pd(YMM_{13}, YMM_{14});

```

where the constants 12 and 33 are masks to control the blend, and permute operations and scalar is a pre-computed array containing the self scalar products  $\langle \mu_j, \mu_j \rangle$  for all  $0 \le j < k$ . The broadcast operation sets all components of the register to the same value. After the subtraction YMM<sub>13</sub> contains a vector of four values which are monotonic with the Euclidean distances:

$$[||x_i - \mu_j||, ||x_{i+1} - \mu_j||, ||x_{i+2} - \mu_j||, ||x_{i+3} - \mu_j||]$$

Furthermore, YMM<sub>13</sub> can be compared to the vector YMM<sub>15</sub>, which stores in each component, the minimal previously found distance to a centroid (i.e., among all centroids  $\mu_{j'}$  with j' < j). We use the component-wise minimum operation \_mm256\_min\_pd, which simultaneously compares the four components of YMM<sub>13</sub> to those of YMM<sub>15</sub>.

### 3.4 Cluster ID Coding

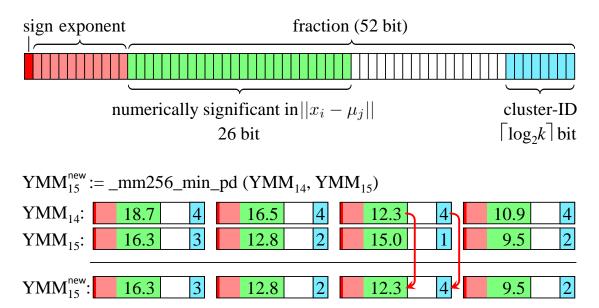

However, our goal here is to keep track of the minimum distance for each point of  $x_i$  but also for the cluster-ID j, which caused the minimum distance. More formally, the main result of the assignment step of the K-means algorithm is for each point  $x_i$  the cluster-ID, which is  $\min_j ||x_i - \mu_j||$ . Our idea to achieve this with clever use of the AVX SIMD operations and without any expensive branching operations (which cause a break in the processor's operation pipeline if the branch prediction fails) to code the cluster-ID directly in the distance value. According to the IEEE-754 specification, double-precision floating-point values are represented using a 52-bit fraction (sometimes also called the mantissa), an 11-bit exponent, and a sign (1 bit), cf. Figure 3.3. For cluster-ID coding, we use a number  $\lceil \log_2(k) \rceil$  of the least significant bits of the fraction. This coding does not change the distance value significantly anyway (if k = 8 and the distance is 1.0, our ID coding changes the distance value to 1.000000000000001). Nevertheless, a numerical

Figure 3.3: Cluster ID coding in IEEE-754 format.

analysis of the Euclidean distance reveals that only roughly half of the fraction bits are numerically significant (in our example, the distance is only known to be between 1.0 and 1.000000015). Therefore, even for unrealistically large k in the order of a million ( $\approx 2^{20}$ ) our coding affects only that part of the fraction, which is numerically insignificant and thus filled with random bits. We use the AVX operations for bitwise logic operations ("and", "and not", "or") for our cluster-ID coding (including the final minimum-operation):

```

\begin{split} & YMM_{14} := \_mm256\_broadcast\_sd(2^{\lceil log_2(k) \rceil} - 1); \\ & YMM_{13} := \_mm256\_andnot\_pd(YMM_{14}, YMM_{13}); \\ & YMM_{14} := \_mm256\_broadcast\_sd(\textit{j} + 0); \\ & YMM_{14} := \_mm256\_or\_pd(YMM_{14}, YMM_{13}); \\ & YMM_{15} := \_mm256\_min\_pd(YMM_{15}, YMM_{14}); \end{split}

```

The operation \_mm256\_broadcast\_sd sets all four components to the same value, a globally constant mask with those bits set that have to take over the cluster-ID.

The impact of the final operation \_mm256\_min\_pd is visualized in the lower part of Figure 3.3: Both YMM<sub>14</sub> and YMM<sub>15</sub> contain four distance values with backpacked cluster IDs each (the color scheme corresponds to the upper part of Figure 3.3 but we

now use the decimal representation of distances and cluster IDs). Applying the minoperation leads to a modification of the third component of YMM<sub>15</sub>, the only component in which YMM<sub>14</sub> is less than YMM<sub>15</sub>. But the minimum operation does not only copy the distance (12.3) from YMM<sub>14</sub> to YMM<sub>15</sub> but also the corresponding cluster-ID (4). The consolidation step for the Euclidean distance and the coding step for the cluster-ID is also repeated for the comparison of the four current data points to  $\mu_{j+1}$ , (stored in the registers YMM<sub>2</sub> and YMM<sub>3</sub>),  $\mu_{j+2}$  (YMM<sub>4</sub>, YMM<sub>5</sub>), and  $\mu_{j+3}$  (YMM<sub>6</sub>, YMM<sub>7</sub>), respectively. After finishing the j-loop, YMM<sub>15</sub> contains the final minimum distances and the corresponding coded cluster IDs, which can be extracted again using the mask operation:

```

YMM<sub>14</sub> := _mm256_broadcast_sd(2^{\lceil \log_2(k) \rceil} - 1);

YMM<sub>15</sub> := _mm256_and_pd(YMM<sub>14</sub>, YMM<sub>15</sub>);

x_{i,...,i+3}.CID := YMM<sub>15</sub>;

```

These 4 cluster IDs are then immediately used to update the statistics (count and sum) in private variables for each thread, again using the AVX operation \_mm256\_add\_pd. Note that this step causes no branching either. Therefore, apart from loops, our algorithm is completely free from branching statements like *if*, *switch*, etc.

### Equivalence to Standard K-means

The assignment step is guarantees to assign each point  $x_i$  to  $\min_j ||x_i - \mu_j||$ , identically for MKM and standard K-means. Each thread collects the sufficient statistics locally, but they are consolidated before using them in the next iteration. Therefore, in every iteration, we obtain the same centroids as standard K-means. Our algorithm MKM is equivalent to standard K-means. If we assume a common initialization for the centroids, both algorithms converge to the same result requiring the same number of iterations.

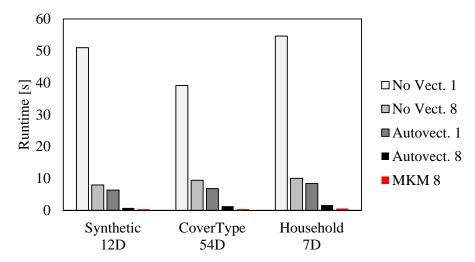

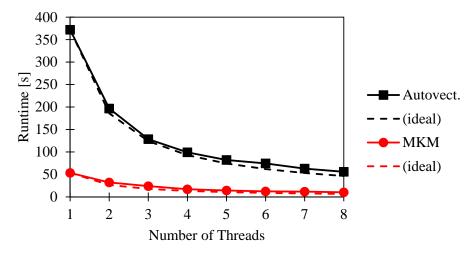

### 3.5 Experiments

**Microarchitecture.** All experiments were performed on a quad-core CPU E5-2609 (Sandy Bridge micro-architecture) featuring AVX1. This CPU has a cache size of  $4 \times 32$  KB (L1 instruction cache),  $4 \times 32$  KB (L1 data cache),  $4 \times 256$  KB (L2 cache), and 10 MB (shared L3 cache). The latency for load operations from L1 cache to registers is 4 clock

3.5. EXPERIMENTS 25

cycles, with a load bandwidth of 32 bytes per cycle. Reading from L2 cache has a latency of 11 clock cycles and a bandwidth of 32 bytes per cycle. Our workstation has two such CPUs on shared memory, so 8 cores are maximally available. All algorithms have been implemented in C++ and compiled with the GNU g++ compiler version 4.7.1. This compiler uses the current SSE version as default. The usage of AVX must be specified as a compiler flag.

**Data.** The synthetic experiments have been performed on randomly generated data with d = 20 and k = 40 whenever not otherwise specified. The number of iterations in Kmeans depends on the initialization and the structure of the optimization surface. It can vary greatly even for data originating from a typical data distribution but sampled with different numbers of objects. Although the number of iterations is always guaranteed to be identical when comparing all versions of multi-core K-means with standard K-means within a given configuration (i.e. number of objects n, number of clusters k, number of dimensions d, etc.) we want also to facilitate comparison across configurations and we therefore report the time required for 5 iterations whenever not otherwise specified. Besides synthetic data, we used two real data sets from the UCI Machine Learning Repository [78]. In our experiments on real data, we run MKM until convergence to get an impression of the practice's runtime behavior. The Forest Covertype data consists of 581,012 instances characterized by 54 attributes. The instances are labeled into 7 classes representing different forest cover types. The Household data consists of 2,049,280 instances described by 7 numerical attributes. We removed instances with missing values from the original data. For Covertype, we set k to the number of classes and clustered the Household data with k = 8.

### Comparison to Standard K-means.